## Lecture Notes in Computer Science Edited by G. Goos, J. Hartmanis, and J. van Leeuwen 2622

Springer

Berlin

Heidelberg

New York

Barcelona

Hong Kong

London

Milan MilanParis Tokyo

# Compiler Construction

12th International Conference, CC 2003 Held as Part of the Joint European Conferences on Theory and Practice of Software, ETAPS 2003 Warsaw, Poland, April 7-11, 2003 Proceedings

#### Series Editors

Gerhard Goos, Karlsruhe University, Germany Juris Hartmanis, Cornell University, NY, USA Jan van Leeuwen, Utrecht University, The Netherlands

Volume Editor

Görel Hedin Lund University, Department of Computer Science Box 118, 221 00 Lund, Sweden E-mail:gorel.hedin@cs.lth.se

Cataloging-in-Publication Data applied for

A catalog record for this book is available from the Library of Congress.

Bibliographic information published by Die Deutsche Bibliothek. Die Deutsche Bibliothek lists this publication in the Deutsche Nationalbibliografie; detailed bibliographic data is available in the Internet at <a href="http://dnb.ddb.de">http://dnb.ddb.de</a>>.

CR Subject Classification (1998): D.3.4, D.3.1, F.4.2, D.2.6, F.3, I.2.2

ISSN 0302-9743 ISBN 3-540-00904-3 Springer-Verlag Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer-Verlag. Violations are liable for prosecution under the German Copyright Law.

Springer-Verlag Berlin Heidelberg New York a member of BertelsmannSpringer Science+Business Media GmbH

http://www.springer.de

$\ensuremath{\mathbb{C}}$  Springer-Verlag Berlin Heidelberg 2003 Printed in Germany

Typesetting: Camera-ready by author, data conversion by PTP-Berlin GmbH Printed on acid-free paper SPIN: 10872988 06/3142 543210

#### Foreword

ETAPS 2003 was the sixth instance of the European Joint Conferences on Theory and Practice of Software. ETAPS is an annual federated conference that was established in 1998 by combining a number of existing and new conferences. This year it comprised five conferences (FOSSACS, FASE, ESOP, CC, TACAS), 14 satellite workshops (AVIS, CMCS, COCV, FAMAS, Feyerabend, FICS, LDTA, RSKD, SC, TACoS, UniGra, USE, WITS and WOOD), eight invited lectures (not including those that are specific to the satellite events), and several tutorials. We received a record number of submissions to the five conferences this year: over 500, making acceptance rates fall below 30% for every one of them. Congratulations to all the authors who made it to the final program! I hope that all the other authors still found a way of participating in this exciting event and I hope you will continue submitting.

A special event was held to honour the 65th birthday of Prof. Wlad Turski, one of the pioneers of our young science. The deaths of some of our "fathers" in the summer of 2002 — Dahl, Dijkstra and Nygaard — reminded us that Software Science and Technology is, perhaps, no longer that young. Against this sobering background, it is a treat to celebrate one of our most prominent scientists and his lifetime of achievements. It gives me particular personal pleasure that we are able to do this for Wlad during my term as chairman of ETAPS.

The events that comprise ETAPS address various aspects of the system development process, including specification, design, implementation, analysis and improvement. The languages, methodologies and tools which support these activities are all well within its scope. Different blends of theory and practice are represented, with an inclination towards theory with a practical motivation on the one hand and soundly based practice on the other. Many of the issues involved in software design apply to systems in general, including hardware systems, and the emphasis on software is not intended to be exclusive.

ETAPS is a loose confederation in which each event retains its own identity, with a separate program committee and independent proceedings. Its format is open-ended, allowing it to grow and evolve as time goes by. Contributed talks and system demonstrations are in synchronized parallel sessions, with invited lectures in plenary sessions. Two of the invited lectures are reserved for "unifying" talks on topics of interest to the whole range of ETAPS attendees. The aim of cramming all this activity into a single one-week meeting is to create a strong magnet for academic and industrial researchers working on topics within its scope, giving them the opportunity to learn about research in related areas, and thereby to foster new and existing links between work in areas that were formerly addressed in separate meetings.

ETAPS 2003 was organized by Warsaw University, Institute of Informatics, in cooperation with the Foundation for Information Technology Development, as well as:

- European Association for Theoretical Computer Science (EATCS);

- European Association for Programming Languages and Systems (EAPLS);

- European Association of Software Science and Technology (EASST); and

#### ACM SIGACT, SIGSOFT and SIGPLAN.

The organizing team comprised:

Mikołaj Bojańczyk, Jacek Chrząaszcz, Piotr Chrząastowski-Wachtel, Grzegorz Grudziński, Kazimierz Grygiel, Piotr Hoffman, Janusz Jabłonowski, Mirosław Kowaluk, Marcin Kubica (publicity), Sławomir Leszczyński (www), Wojciech Moczydłowski, Damian Niwiński (satellite events), Aleksy Schubert, Hanna Sokołowska, Piotr Stańczyk, Krzysztof Szafran, Marcin Szczuka, Łukasz Sznuk, Andrzej Tarlecki (co-chair), Jerzy Tiuryn, Jerzy Tyszkiewicz (book exhibition), Paweł Urzyczyn (co-chair), Daria Walukiewicz-Chrząaszcz, Artur Zawłocki.

ETAPS 2003 received support from:<sup>1</sup>

- Warsaw University

- European Commission, High-Level Scientific Conferences and Information Society Technologies

- US Navy Office of Naval Research International Field Office,

- European Office of Aerospace Research and Development, US Air Force

- Microsoft Research

Overall planning for ETAPS conferences is the responsibility of its Steering Committee, whose current membership is:

Egidio Astesiano (Genoa), Pierpaolo Degano (Pisa), Hartmut Ehrig (Berlin), José Fiadeiro (Leicester), Marie-Claude Gaudel (Paris), Evelyn Duesterwald (IBM), Hubert Garavel (Grenoble), Andy Gordon (Microsoft Research, Cambridge), Roberto Gorrieri (Bologna), Susanne Graf (Grenoble), Görel Hedin (Lund), Nigel Horspool (Victoria), Kurt Jensen (Aarhus), Paul Klint (Amsterdam), Tiziana Margaria (Dortmund), Ugo Montanari (Pisa), Mogens Nielsen (Aarhus), Hanne Riis Nielson (Copenhagen), Fernando Orejas (Barcelona), Mauro Pezzè (Milano), Andreas Podelski (Saarbrücken), Don Sannella (Edinburgh), David Schmidt (Kansas), Bernhard Steffen (Dortmund), Andrzej Tarlecki (Warsaw), Igor Walukiewicz (Bordeaux), Herbert Weber (Berlin).

I would like to express my sincere gratitude to all of these people and organizations, the program committee chairs and PC members of the ETAPS conferences, the organizers of the satellite events, the speakers themselves, and Springer-Verlag for agreeing to publish the ETAPS proceedings. The final votes of thanks must go, however, to Andrzej Tarlecki and Pawel Urzyczyn. They accepted the risk of organizing what is the first edition of ETAPS in Eastern Europe, at a time of economic uncertainty, but with great courage and determination. They deserve our greatest applause.

Leicester, January 2003

José Luiz Fiadeiro ETAPS Steering Committee Chair

<sup>&</sup>lt;sup>1</sup> The contents of this volume do not necessarily reflect the positions or the policies of these organizations and no official endorsement should be inferred.

#### **Preface**

The International Conference on Compiler Construction (CC) is concerned with recent developments in compiler construction, programming language implementation, and language design. It addresses work on all phases of compilation and for all language paradigms, emphasizing practical and efficient methods and tools. The broad area of compiler construction is reflected in these proceedings. The papers cover the full range of compiler topics including compiler tools, parsing, type analysis, static analysis, code optimization, register allocation, and run-time issues.

CC 2003 was held in Warsaw, Poland during 5–13 April 2003 and was the 12th conference in the series. This year, submissions reached a record number of 83 papers of which 77 were regular papers and 6 were short tool demonstration papers. Of these, 20 regular papers and one tool demonstration paper were selected for presentation and are included in these proceedings.

The proceedings also include two invited papers. The CC 2003 invited speaker was Barbara Ryder, whose talk was entitled *Dimensions of Precision in Reference Analysis of Object-Oriented Programming Languages*. In addition, we have the honor of including the paper by Tony Hoare who gave one of the two ETAPS "unifying" invited talks. The title of his talk was *The Verifying Compiler: a Grand Challenge for Computing Research*.

The selection of papers took place at an intense program committee meeting in Lund, Sweden, on December 6th, 2002. Eight of the PC members attended the meeting, and another seven joined in the discussion via a telephone conference call. I wish to thank all my colleagues on the program committee for their hard work, detailed reviews, and friendly cooperation. I am especially grateful to Nigel Horspool, Reinhard Wilhelm, and Evelyn Duesterwald, who, as members of the CC steering committee, gave me prompt advice whenever I needed it throughout the process of being the program chair. Many thanks also to the large number of additional reviewers who helped us read and evaluate the submitted papers.

Many people helped me in the administration of the PC work. In particular, I wish to thank Jonas Wisbrant for being very helpful in the organization of the program committee meeting and arranging a simple but very useful web facility for the PC members participating via telephone. Thanks also to Christian Andersson who helped me assemble these proceedings, and to Tiziana Margaria and Martin Karusseit at METAframe for their support of the electronic online conference system we used for submissions and reviewing. Finally, I wish to thank José Luiz Fiadeiro and the ETAPS team for their excellent organization and coordination of the whole ETAPS event.

Lund, January 2003

Görel Hedin

#### **Program Committee**

Uwe Aßmann (Linköpings Universitet, Sweden) Isabelle Attali (INRIA Sophia Antipolis, France) Judith Bishop (University of Pretoria, South Africa)

Mark van den Brand (CWI, The Netherlands) Peter Dickman (University of Glasgow, UK)

Evelyn Duesterwald (IBM T.J. Watson Research Center, USA)

Tibor Gyimothy (University of Szeged, Hungary) Görel Hedin – Chair (Lund University, Sweden) Nigel Horspool (University of Victoria, Canada) Uwe Kastens (Universität Paderborn, Germany)

Oege de Moor (Oxford University, UK) Mooly Sagiv (Tel Aviv University, Israel)

Vivek Sarkar (IBM T.J. Watson Research Center, USA)

Pierluigi San Pietro (Politecnico di Milano, Italy) Reinhard Wilhelm (Saarland University, Germany)

Jan Vitek (Purdue University, USA)

Jingling Xue (University of New South Wales, Australia)

#### **Additional Reviewers**

Peter Faber

Chap Flack

Rudolf Ferenc

Hila Fatal

Giampaolo Agosta Guang Gao Tamas Gergely John Avcock Françoise Baude Christian Grothoff Joerg Bauer David Grove Nick Benton Flavius Gruian David Bernstein Charles Hardnett Rastislav Bodik Ferenc Havasi Qiong Cai Roger Henriksson Calin Cascaval Ludovic Henrio Siddhartha Chatterjee Michael Hind Alessandra Cherubini Qingguang Huang Roberto Costa Anders Ive Pascal Degenne Barry Jay Stephan Diehl Akos Kiss Julian Dolby Karsten Klohs Nurit Dor Jens Knoop Kemal Ebcioglu Jochen Kreimer Erik Eckstein Uli Kremer Torbjörn Ekman David Lacey

Ralf Laemmel

Marc Langenbach

Ken Friis Larsen Dinh Khoi Le Gabor Lehotai Joao Saraiva

Annie Liu Carsten Schmidt

Gabor Loki Bernhard Scholz

Philipp Lucas Bernard Paul Serpette

Eric Madelaine Peter Sestoft Roman Manevich Ran Shaham Vincenzo Martena Yefim Shuf

Pierre-Etienne Moreau Ganesh Sittampalam Angelo Morzenti Jonas Skeppstedt Albert Nymeyer Adrian Slowik Pieter Olivier Doaitse Swierstra Santosh Pande Stephan Thesing David Pereira Peter Thiemann Erez Petrank Frank Tip Peter Pfahler Xavier Vera Matteo Pradella Jurgen Vinju Christian Probst Joost Visser Giuseppe Psaila Sebastian Winkel

Stefano Crespi Reghizzi Peng Wu

Tobias Ritzau Eran Yahav

Tom Rothamel Greta Yorsh

Gilles Roussel Olivier Zendra

## Table of Contents

| Register Allocation                                                                                        |     |

|------------------------------------------------------------------------------------------------------------|-----|

| Combined Code Motion and Register Allocation Using the Value State Dependence Graph                        | 1   |

| Early Control of Register Pressure for Software Pipelined Loops  Sid-Ahmed-Ali Touati, Christine Eisenbeis | 17  |

| Register Allocation by Optimal Graph Coloring                                                              | 33  |

| Language Constructs and Their Implementation                                                               |     |

| A Compilation and Optimization Model for Aspect-Oriented                                                   |     |

| Programs                                                                                                   | 46  |

| A Pattern Matching Compiler for Multiple Target Languages                                                  | 61  |

| A New One-Pass Transformation into Monadic Normal Form                                                     | 77  |

| Type Analysis                                                                                              |     |

| Run-Time Type Checking for Binary Programs                                                                 | 90  |

| Precision in Practice: A Type-Preserving Java Compiler                                                     | 106 |

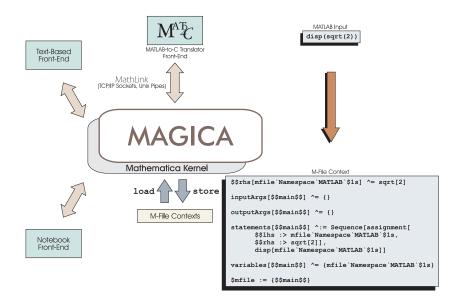

| The MAGICA Type Inference Engine for MATLAB $^{\circledR}$                                                 | 121 |

| CC Invited Talk                                                                                            |     |

| Dimensions of Precision in Reference Analysis of Object-Oriented Programming Languages                     | 126 |

| Java                                                                                                       |     |

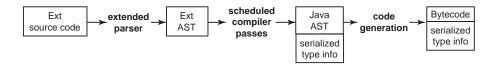

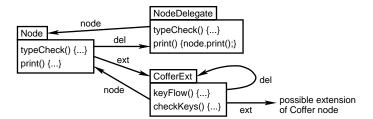

| Polyglot: An Extensible Compiler Framework for Java                                                        | 138 |

| Scaling Java Points-to Analysis Using Spark                                                          | 153 |

|------------------------------------------------------------------------------------------------------|-----|

| Effective Inline-Threaded Interpretation of Java Bytecode Using Preparation Sequences                | 170 |

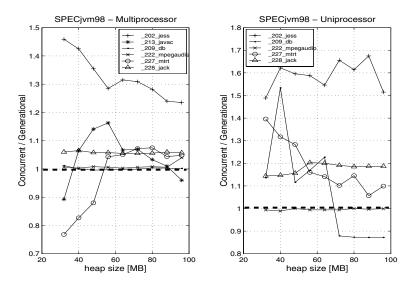

| Integrating Generations with Advanced Reference Counting Garbage Collectors                          | 185 |

| Pot Pourri                                                                                           |     |

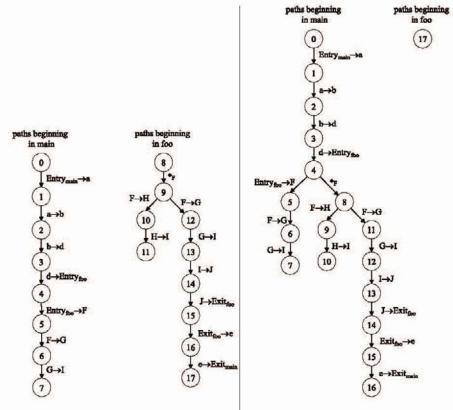

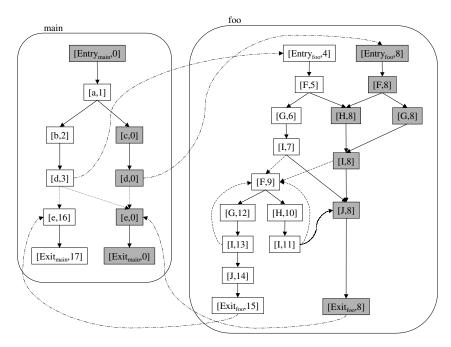

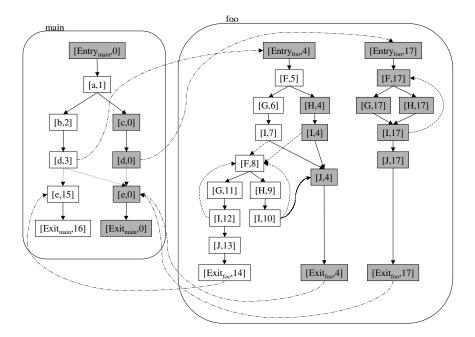

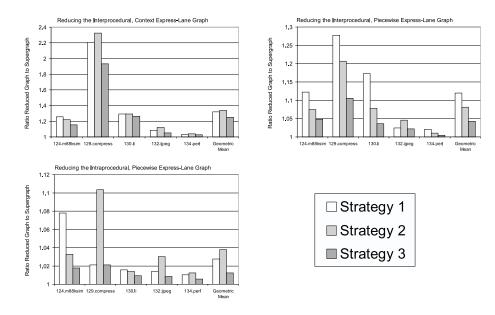

| The Interprocedural Express-Lane Transformation                                                      | 200 |

| Automatic Detection of Uninitialized Variables                                                       | 217 |

| Generalised Regular Parsers                                                                          | 232 |

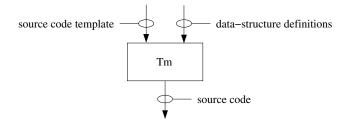

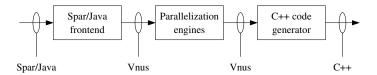

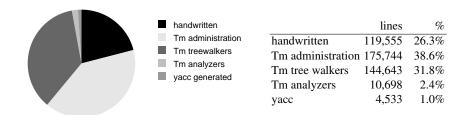

| Rapid and Robust Compiler Construction Using Template-Based Metacompilation                          | 247 |

| ETAPS Invited Talk                                                                                   |     |

| The Verifying Compiler: A Grand Challenge for Computing Research<br>$Tony\ Hoare$                    | 262 |

| Optimization                                                                                         |     |

| Address Register Assignment for Reducing Code Size                                                   | 273 |

| Offset Assignment Showdown: Evaluation of DSP Address Code Optimization Algorithms                   | 290 |

| Integrating High-Level Optimizations in a Production Compiler:  Design and Implementation Experience | 303 |

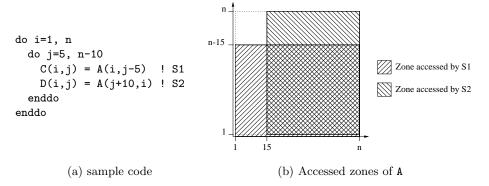

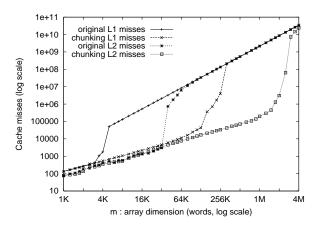

| Improving Data Locality by Chunking                                                                  | 320 |

| Author Index                                                                                         | 335 |

## Combined Code Motion and Register Allocation Using the Value State Dependence Graph

Neil Johnson and Alan Mycroft

Computer Laboratory, University of Cambridge William Gates Building, JJ Thompson Avenue, Cambridge, CB3 0FD, UK {Neil.Johnson,Alan.Mycroft}@cl.cam.ac.uk

**Abstract.** We define the Value State Dependence Graph (VSDG). The VSDG is a form of the Value Dependence Graph (VDG) extended by the addition of state dependence edges to model sequentialised computation. These express store dependencies and loop termination dependencies of the original program. We also exploit them to express the additional serialization inherent in producing final object code.

The central idea is that this latter serialization can be done incrementally so that we have a class of algorithms which effectively interleave register allocation and code motion, thereby avoiding a well-known phase-order problem in compilers. This class operates by first normalizing the VSDG during construction, to remove all duplicated computation, and then repeatedly choosing between: (i) allocating a value to a register, (ii) spilling a value to memory, (iii) moving a loop-invariant computation within a loop to avoid register spillage, and (iv) statically duplicating a computation to avoid register spillage.

We show that the classical two-phase approach (code motion then register allocation in both Chow and Chaitin forms) are examples of this class, and propose a new algorithm based on depth-first cuts of the VSDG.

#### 1 Introduction

An important problem encountered by compiler designers is the *phase order-* ing problem, which can be phrased as "in which order does one schedule the register allocation and code motion phases to give the best target code?". These phases are antagonistic to each other—code motion may increase register pressure, while register allocation places additional dependencies between instructions, artificially constraining code motion. In this paper we show that a unified approach, in which both register allocation and code motion are considered together, sidesteps the problem of which phase to do first.

In support of this endeavour, we present a new program representation, the Value State Dependence Graph (VSDG), as an extension of the Value Dependence Graph (VDG) [21]. It is a simple unifying framework within which a wide range of code space optimizations can be implemented. We believe that the VSDG can be used in both intermediate code transformations, and all the way through to final target code generation.

Traditional register allocation has been represented as a graph colouring problem, originally proposed by Chaitin [5], and based on the Control Flow Graph (CFG). Unfortunately the CFG imposes an artificial ordering of instructions, constraining the register allocator to the given order.

The VDG represents programs as value dependencies—there is an edge (p, n), drawn as an arrow  $n \to p$ , if node n requires the value of p to compute its own value. This representation removes any specific ordering of instructions (nodes), but does not elegantly handle loop and function termination dependencies.

The VSDG introduces state dependency edges to model sequentialised computing. These edges also have the surprising benefit of generalising the VSDG: by adding sufficient serializing edges we can select any one of a number of CFGs. Our thesis is that relaxing the exact serialization of the CFG into the more general VSDG supports a combined register allocation and code motion algorithm.

#### 1.1 Paper Structure

This paper is structured as follows. Section 2 describes the forms of nodes and edges in the VSDG, while Section 3 explores additional serialization and liveness within the VSDG. In Section 4 we describe the general approach to joint register allocation and code motion (RACM) as applied to the VSDG, and show that classical Chaitin/Chow-style register colouring specialises it. Section 5 introduces our new greedy register allocation algorithm. Section 6 provides context for this paper with a review of related work, with Section 7 concluding.

#### 2 Formalism

The Value State Dependence Graph is a directed graph consisting of operation nodes, loop and merge nodes together with value- and state-dependency edges. Cycles are permitted but must satisfy various restrictions. A VSDG represents a single procedure; this matches the classical CFG but differs from the VDG in which loops were converted to tail-recursive procedures called at the logical start of the loop. We justify this because of our interest in performing RACM at the same time; inter-procedural motion and allocation issues are considered a topic for future work.

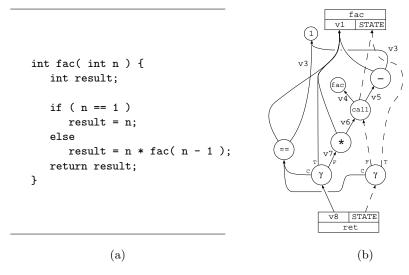

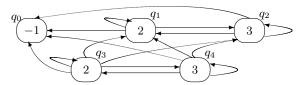

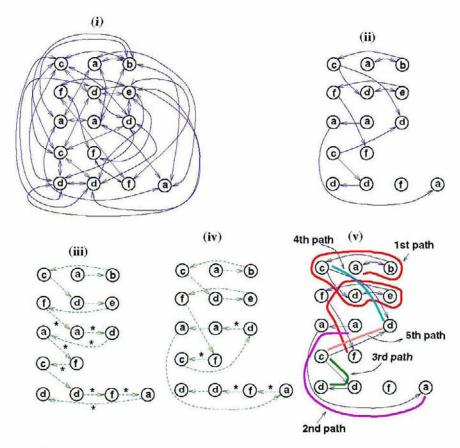

An example VSDG is shown in Fig. 1. In (a) we have the original C source for a recursive factorial function. The corresponding VSDG (b) shows both value and state edges and a selection of nodes.

#### 2.1 Definition of the VSDG

**Definition 1.** A VSDG is a labelled directed graph  $G = (N, E_V, E_S, \ell, N_0, N_\infty)$  consisting of nodes N (with unique entry node  $N_0$  and exit node  $N_\infty$ ), value-dependency edges  $E_V \subseteq N \times N$ , state-dependency edges  $E_S \subseteq N \times N$ . The labelling function  $\ell$  associates each node with an operator (§2.2 for details).

Fig. 1. A recursive factorial function, whose VSDG illustrates the key graph components—value dependency edges (solid lines), state dependency edges (dashed lines), a const node, a call node, two  $\gamma$ -nodes, a conditional node (==), and the function entry and exit nodes. The left-hand  $\gamma$ -node returns the original function argument if the condition is true, or that of the expression otherwise. The right-hand  $\gamma$ -node behaves similarly for the state edges, returning either the state on entry to the function, or that returned by the call node.

VSDGs have to satisfy two well-formedness conditions. Firstly  $\ell$  and the  $(E_V)$  arity must be consistent, e.g. that a binary arithmetic operator must have two inputs; secondly (at least for the purposes of this paper) that the VSDG corresponds to a structured program, e.g. that there are no cycles in the VSDG except those mediated by  $\theta$  (loop) nodes (see §3.2).

Value dependency  $(E_V)$  indicates the flow of values between nodes, and must be preserved during register allocation and code motion.

State dependency  $(E_S)$ , for this paper, represents two things; the first is essential sequential dependency required by the original program, e.g. a given load instruction may be required to follow a given store instruction without being re-ordered, and a return node in general must wait for an earlier loop to terminate even though there might be no value-dependency between the loop and the return node. The second purpose, which in a sense is the centre of this work, is that state-dependency edges can be added incrementally until the VSDG corresponds to a unique CFG ( $\S 3.1$ ). Such state dependency edges are called serializing edges.

An edge  $(n_1, n_2)$  represents the flow of data or control from  $n_1$  to  $n_2$ , i.e. in the forwards data flow direction, so we will see  $n_1$  as a predecessor of  $n_2$ . Similarly we will regard  $n_2$  as a successor of  $n_1$ . If we wish to be specific we will write V-successors or S-successors for respectively  $E_V$  and  $E_S$  successors.

#### N. Johnson and A. Mycroft

Similarly, we will write  $succ_V(n)$ ,  $pred_S(n)$  and the like for appropriate sets of successors or predecessors, and dom(n) and pdom(n) for sets of dominators and post-dominators respectively. We will draw pictures in the VDG form, with arrows following the *backwards data flow direction*, so that the edge  $(n_1, n_2)$  will be represented as an arrow  $from n_2$  to  $n_1$ .

The VSDG inherits from the VDG the property that a program is implicitly represented in Static Single Assignment (SSA) form [8]: a given operator node, n, will have zero or more  $E_V$ -successors using its value. Note that, in implementation terms, a single register can hold the produced value for consumption at all successors; it is therefore useful to talk about the idea of an output port for n being allocated a specific register, r, to abbreviate the idea of r being used for each edge  $(n_1, n_2)$  where  $n_2 \in succ(n_1)$ . Similarly, we will talk about (say) the "right-hand input port" of a subtraction instruction, or of the R-input of a  $\theta$ -node.

#### 2.2 Node Labelling with Instructions

There are four main classes of VSDG nodes, based on those of the triVM Intermediate Language [13]: value nodes (representing pure arithmetic),  $\gamma$ -nodes (conditionals),  $\theta$ -nodes (loops), and state nodes (side-effects).

- **2.2.1** Value Nodes. The majority of nodes in a VSDG generate a value based on some computation (add, subtract, etc) applied to their dependent values (constant nodes, which have no dependent nodes, are a special case).

- **2.2.2**  $\gamma$ -Nodes. Our  $\gamma$ -node is similar to the  $\gamma$ -node of Gated Single Assignment form [2] in being dependent on a control predicate, rather than the control-independent nature of SSA  $\phi$ -functions.

**Definition 2.** A  $\gamma$ -node  $\gamma(C, T, F)$  evaluates the condition dependency C, and returns the value of T if C is true, otherwise F.

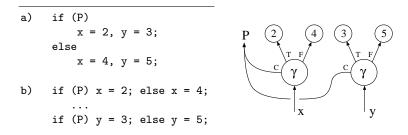

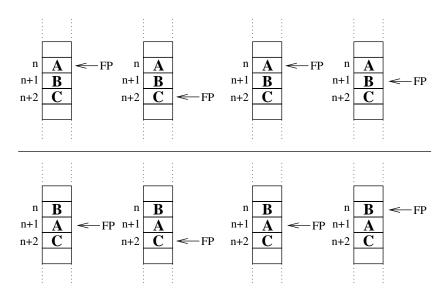

We generally treat  $\gamma$ -nodes as single-valued nodes (constrast  $\theta$ -nodes, which are treated as tuples), with the effect that two separate  $\gamma$ -nodes with the same condition can be later combined (Section 4) into a tuple using a single test. Fig. 2 illustrates two  $\gamma$ -nodes that can be combined in this way.

- **2.2.3**  $\theta$ -Nodes. The  $\theta$ -node models the iterative behaviour of loops, modelling loop state with the notion of an *internal value* which may be updated on each iteration of the loop. It has five specific ports which represent dependencies at various stages of computation.

- **Definition 3.** A  $\theta$ -node  $\theta(C, I, R, L, X)$  sets its internal value to initial value I then, while condition value C holds true, sets L to the current internal value and updates the internal value with the repeat value R. When C evaluates to false computation ceases and the last internal value is returned through the X port.

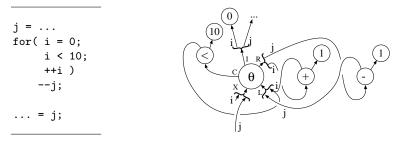

A loop which updates k variables will have: a single condition port C, initial-value ports  $I_1, \ldots, I_k$ , loop iteration ports  $L_1, \ldots, L_k$ , loop return ports  $R_1, \ldots, R_k$ , and loop exit ports  $X_1, \ldots, X_k$ . The example in Fig. 3 shows a pair (2-tuple) of values being used for I, R, L, X, one for each loop-variant value.

For some purposes the L and X ports could be fused, as both represent outputs within, or exiting, a loop (the values are identical, while the C input merely selects their routing). We avoid this for two reasons: (i) we have operational semantics for VSDGs G and these semantics require separation of these concerns; and (ii) our construction of  $G^{noloop}$  (§3.2) requires it.

The  $\theta$ -node directly implements pre-test loops (while, for); post-test loops (do...while, repeat...until) are synthesised from a pre-test loop preceded by a duplicate of the loop body. At first this may seem to cause unnecessary duplication of code, but it has two important benefits: (i) it exposes the first loop body iteration to optimization in post-test loops (cf. loop-peeling), and (ii) it normalizes all loops to one loop structure, which both reduces the cost of optimization, and increases the likelihood of two schematically-dissimilar loops being isomorphic in the VSDG.

**2.2.4** State Nodes. Loads, stores, and their volatile equivalents, compute a value and/or state (non-volatile loads return a value from memory without generating a new state). Accesses to volatile memory or hardware can change state independently of compiler-aware reads or writes (*cf.* IO-state [7]).

The call node takes both the name of the function to call and a list of arguments, and returns a list of results; it is treated as a state node as the function body may read or update state.

We maintain the simplicity of the VSDG by imposing the restriction that all functions have one return node (the exit node  $N_{\infty}$ ), which returns at least one result (which will be a state value in the case of void functions). To ensure that function calls and definitions are colourable, we suppose that the number of arguments to, and results from, a function is smaller than the number of physical registers—further arguments can be passed via a stack as usual.

Fig. 2. Two different code schemes (a) & (b) map to the same  $\gamma$ -node structure.

Fig. 3. A  $\theta$ -node example showing a for loop. Evaluating the  $\theta$ -node's **X** port triggers it to evaluate the **I** value (outputting the value on the **L** port). While **C** evaluates to true, it evaluates the **R** value (which in this case also uses the  $\theta$ -node's **L** value). When **C** is false, it returns the final internal value through the **X** port. As **i** is not used after the  $\theta$ -node loop then there is no dependency on the **i** port of **X**.

Note also that the VSDG neither forces loop invariant code into nor out-of loop bodies, but rather allows later phases to determine, by adding serializing edges, such placement of loop invariant nodes for later phases.

#### 3 Applying the VSDG to RACM

#### 3.1 Serialization

Weise et al. [21] observe that their mapping from CFGs to VDGs is manyone; that paper also suggests that "Code motion optimizations are decided when the demand dependence graph is constructed from the VDG"—i.e. that a VDG should be mapped back into a CFG for further processing—but does not give an algorithm or consider which of the many CFGs corresponding to a VSDG should be selected.

We identify VSDGs with 'enough' serializing edges with CFGs—such VSDGs can be simply transformed into CFGs if desired—the task of RACM then being to make the VSDG sufficiently sequential. The following informal definition captures this idea for the purposes of this paper.

**Definition 4.** A sequential VSDG is one which has enough serializing edges to make it correspond to a single CFG.

Here 'enough' means in essence that each node in the VSDG has a unique  $(E_V \cup E_S)$  immediate dominator which can be seen as its predecessor in the CFG. Exceptions arise for the start node (which has no predecessors in the VSDG or corresponding CFG),  $\gamma$ -nodes and  $\theta$ -nodes. Given a  $\gamma$ -node, we interpret those nodes which the T port post-dominates as the *condition-true* sub-CFG and those which the F port post-dominates as the *condition-false* sub-CFG; a control-split node (corresponding to a CFG test node) is added to the VSDG as the immediate  $E_S$ -dominator of both sub-CFGs. For a  $\theta$ -node, we recursively require this sequential property for its body, L, and interpret the "unique immediate dominator" property as a constraint on its I port.

#### 3.2 VSDG Well-Formedness

As in the VDG we restrict attention to reducible graphs for the VSDG; recall that any CFG can be made reducible by duplicating code or by introducing additional boolean variables. For this paper we further restrict to programs whose only loops are while-loops and which exit them only by the condition becoming *false*, *i.e.* no break and the like (again this could be achieved with code duplication or with additional boolean variables).

In order to specify the "all cycles in a VSDG are mediated by  $\theta$ -nodes" restriction, it is convenient to define a transformation on VSDGs.

**Definition 5.** Given a VSDG, G, we define  $G^{noloop}$  to be identical to G except that each  $\theta$ -node  $\theta_i$  is replaced with two nodes,  $\theta_i^{head}$  and  $\theta_i^{tail}$ ; edges to or from ports I or L of the original  $\theta$ -node are redirected to  $\theta_i^{head}$  whereas those to or from ports R, X, C are redirected to  $\theta_i^{tail}$ .

We then require  $G^{noloop}$  to be an acyclic graph.

When adding serializing edges we must maintain this acyclic property. To serialize nodes connected to a  $\theta$ -node's X port we add serializing edges to  $\theta^{tail}$ ; all nodes within the body of the loop are on the sequential path from  $\theta^{tail}$  to  $\theta^{head}$ ; all other nodes are serialized before  $\theta^{head}$ . Definition 6 below sets out the conditions for a node to be within a loop.

Although this is merely a formal transformation, note that if we interpret  $\theta^{tail}$  as a  $\gamma\text{-node}$  (or possibly a tuple thereof) and interpret  $\theta^{head}$  as an identity operation then  $G^{noloop}$  represents a VSDG in which each loop is executed zero or one times according to the condition. Our  $\theta^{head}$  and  $\theta^{tail}$  nodes, while similar to GSA's  $\mu\text{-}$  and  $\eta^F\text{-}\text{functions}$  [2], avoids the need for their "non-deterministic merge gate" to break cyclic dependencies.

The formal definition of a VSDG being well-formed is then:

**Definition 6.** A VSDG, G, is well-formed if (i)  $G^{noloop}$  is acyclic and (ii) for each pair of  $(\theta^{head}, \theta^{tail})$  nodes in  $G^{noloop}$ ,  $\theta^{tail}$  post-dominates all nodes in  $succ_{V \cup S}^+(\theta^{head}) \cap pred_{V \cup S}^+(\theta^{tail})$ .

The second condition says that no value computed during a loop can be used outside the loop, except via the X port of a  $\theta$ -node.

#### 3.3 VSDG Normalization

The RACM algorithms below will assume (for maximal optimization potential rather than correctness) that the VSDG has been normalized, roughly in the way of 'hash-CONSing': any two nodes which have identical input nodes, will be assumed to have been replaced with a single node provided that this does not violate well-formedness by creating a cycle in the VSDG. Consider

```

int f( int v[], int i ) {

int a = v[i+1];

v[7] = 0;

return v[i+1] + a;

}

```

There will only be one node for the constant 1, and one for the addition of this node to the second formal parameter (i+1) but two nodes for the *loading* from v[i+1] because sharing this node would lead to a cycle in  $E_S$  by being both a predecessor and successor of the *store* to v[7].

Note that this is a safe form of CSE and loop invariant code lifting; this optimization is selectively undone (node cloning) during the joint RACM phase when required by register pressure.

#### 3.4 Liveness in VSDGs

For the purposes of register allocation (*cf.* the register interference graph), we need to know which (output ports of) VSDG nodes may hold values simultaneously so we can forbid them being allocated the same register.

We define a *cut* to be a partition  $N_1 \cup N_2$  of nodes in the VSDG with the property that there is no  $E_V \cup E_S$  edge from  $N_2$  to  $N_1$  (excepting edges from L ports of  $\theta$ -nodes—see the  $G^{noloop}$  construction).

We now define nodes n and n' to *interfere* if there is a cut  $N_1 \cup N_2$  with  $n, n' \in N_1$  and with both succ(n) and succ(n') having non-empty intersections with  $N_2$ .

This generalises the normal concept register of interference in a CFG; there a cut is just a program point and interference means "simultaneously live at any program point". Similarly "virtual register" corresponds to our "output port of a node". Note that we use the concept of "cut based on Depth From Root" in Section 5 for our new greedy algorithm.

#### 4 Register Allocation and Code Motion

The goal of register allocation in the VSDG is to allocate one physical register (from a fairly small set) to each node's output ports.  $\theta$ -nodes are a special case, as they require multiple registers on their tupled I, R, L and X ports.

Register requirements can be reduced by serializing computations (a register can be reused in two independent computations if we know that they do not interleave), or by reducing the range over which a value is live by duplicating a computation or by spilling a value to memory. In both cases the idea is that these operations reduce the register interference.

#### 4.1 A Non-deterministic Approach

Given a VSDG we repeatedly apply the following non-deterministic algorithm until all the nodes are coloured and the VSDG is sequential:

- 1. Colour a port with a physical register—provided no port it interferes with is already coloured with the same register;

- 2. Add a serializing edge to force one node before another—this removes edges from the interference graph by forbidding interleaving of computations;

- 3. Clone a node, *i.e.* recalculate it to reduce register pressure.

- 4. Tunnel values through memory by introducing store/load spill nodes.

- 5. Merge two  $\gamma$ -nodes a and b into a tuple, provided their C ports reference the same node and there is no path from a to b or from b to a.

The first action assigns a physical register to a port of the given node. The second moves the node, with the effect of changing the register usage; the choice of *which* node to move is determinined by specific algorithms (see  $\S4.2$  and Section 5).

Node cloning replaces a single instance of a node that has multiple uses, with multiple copies (clones) of the node, each with a subset of the original dependency edges. For example, a node n with two dependent nodes p and q, can be cloned into n' and n'', with p dependent on n' and q dependent on n''.

Spilling follows the traditional Chaitin-style register spilling where we add store and load nodes, together with some temporary storage in memory.

Finally, because the initial VSDG was normalized to ensure that each  $\gamma$ -node represented the merge of a *single* variable, given a VSDG such as that in Fig. 2, we can either arrange to serialize the two  $\gamma$ -nodes (action 2) resulting in two separate tests (or conditional move instructions) or to merge them (action 5) so that a single test is used (as in Fig. 2(a)).

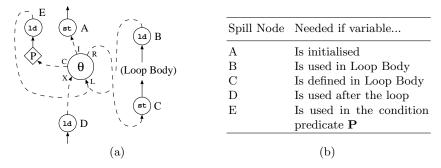

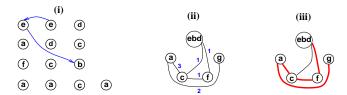

The cost of spilling loop-variant variables is rather higher than the store-andreload for a normal spill. For  $\theta$ -nodes where the tuple is wider than the available target registers, we must spill one or more of the  $\theta$ -node variables over the loop test code, not merely within the loop itself. At most this requires two stores and three loads for each variable spilled. Fig. 4 shows the location of the five spill nodes (a), with table (b) describing the use of each of the spill nodes.

#### 4.2 The Classical Algorithms

We can phrase the classical Chaitin/Chow-style register allocators as instances of the above algorithm:

1. Perform all code motion transforms through adding serializing edges and merging  $\gamma$ -nodes if not already sequentialised;

Fig. 4. Illustrating the locations of the five spill nodes associated with a  $\theta$ -node.

- 2. Map the VSDG onto a CFG by adding additional serializing edges;

- 3. If there are insufficient physical registers to colour a node port, then:

- a) Chaitin-style allocation [5]: spill nodes, with the restriction that the target register of the reload is the same as the source register of the store. Chaitin's cost estimates can be applied to determine which edge to spill;

- b) Chow-style allocation [6]: spill nodes, but without the register restriction of Chaitin-style, thus splitting the live-range of the virtual register; use Chow's heuristics to decide which edge to split.

In both Chaitin and Chow instances post-code-motion transformations during register allocation are limited to inserting store and load nodes into the program.

#### 5 A New Register Allocation Algorithm

The Chaitin/Chow algorithms do not make full use of the dependence information within the VSDG; they assume that a previous phase has performed code motion to produce a sequential VSDG—corresponding to a single CFG—on which traditional register colouring algorithms are applied.

We now present the central point of this paper—a register allocation algorithm specifically designed to maximise the usage of information within the VSDG. The algorithm consists of two distinct phases:

- 1. Starting at the exit node  $N_{\infty}$ , walk up the graph edges calculating the maximal Depth From Root (DFR) of each node (see Definition 7); for each set of nodes of equal depth calculate their liveness width (the number of distinct values on which they depend, taking into account control flow).

- 2. Apply a forward "snow-plough"<sup>1</sup>-like graph reshaping algorithm, starting from  $N_{\infty}$  and pushing up towards  $N_0$ , to ensure that the liveness width is never more than the number of physical resisters. This is achieved by splitting, spilling or adding serializing edges in greedy way so that the previously smoothed-out parts of the graph (nearer the exit) are not re-visited.

The result is a colourable VSDG; colouring it constitutes register assignment completing the algorithm.

#### 5.1 Partitioning the VSDG

The first phase annotates the VSDG with the maximal Depth From Root. The second phase then processes each cut of the VSDG in turn.

**Definition 7.** The maximal Depth From Root,  $\mathcal{D}(n)$ , of a node  $n \in N$  is the length of the longest path  $p \in (E_V \cup E_S)^*$  from the root to n. Loop bodies are traversed once, such that a  $\theta$ -node has two DFRs—one each for the  $\theta$ <sup>head</sup> and  $\theta$ <sup>tail</sup> nodes.

<sup>&</sup>lt;sup>1</sup> Imagine a snow plough pushing forward, scooping up excess snow, and depositing it where there is little snow. The goal is to even out the peaks and troughs.

**Definition 8.** A depth-first cut  $S_{=d}$  is the set of nodes with the same DFR d:

$$\mathcal{S}_{=d} = \{ n \in N \mid \mathcal{D}(n) = d \}$$

It is convenient also to write

$$S_{\leq d} = \{ n \in N \mid \mathcal{D}(n) \leq d \}$$

$$S_{>d} = \{ n \in N \mid \mathcal{D}(n) > d \}$$

Note that the partition  $(S_{\leq d}, S_{\geq d})$  is a *cut* according to the definition of §3.4.

Computing the DFR of a given VSDG is equivalent to computing the depthfirst search of the graph—we simply start at the root node  $N_{\infty}$  and recursively walk along all dependency edges, setting each node to the larger of the node's current DFR and the new DFR, terminating either at the entry node  $N_0$  or nodes with DFRs greater than the current DFR. It has a complexity of  $O(N+E_V+E_S)$ .

#### 5.2 Calculating Liveness Width

We wish to transform each cut so that the number of nodes having edges passing through it is no greater than  $\mathcal{R}$ , the number of registers available for colouring. For a cut of depth d the set of such live nodes is given by

$$W_{in}(d) = S_{>d} \cap pred_V(S_{\leq d})$$

*i.e.* those nodes which are further than d from the exit node but whose values may be used on the path to the exit node. Note that only  $E_V$  and not  $E_S$  edges count towards liveness.

One might expect that  $|W_{in}(d)|$  is the number of registers required to compute the nodes in  $S_{\leq d}$  but this overstates the number of registers required for conditional nodes.  $\gamma$ -nodes have the property that the edges of each of their selection dependencies are disjoint—on any given execution trace, exactly one path to the  $\gamma$ -node will be executed at a time, and so therefore we can reuse the same registers to colour its True- and False-dominated nodes.

We identify the  $\gamma$ -node dependency register sets using the dominance property thus:

**Definition 9.** A node  $n \in N$  is a predicated node iff it is post-dominated by either the True or the False port of a  $\gamma$ -node, but not by both.

Note that replacing nodes in either of the *True* or *False* regions with no-ops each gives a lower-bound to the liveness width of the cut<sup>2</sup>. Moreover, the greater of the liveness widths for these modified VSDGs gives the corrected liveness width for the original VSDG.

We prefer to formulate this in constraint form.

<sup>&</sup>lt;sup>2</sup> Such no-ops are nodes with no value dependencies on input or output, but with state-dependences where previously there was either a value or state edge so that the DFR is not affected.

**Definition 10.** A VSDG is colourable with  $\mathcal{R}$  registers if either:

- 1. Every cut of depth d has  $|W_{in}(d)| \leq \mathcal{R}$ ; or

- 2. Each VSDG resulting from replacing either True or False regions with no-ops satisfies 1.

#### 5.3 Pass through Edges

Some edges (i.e. of lifetime greater than one) pass through a cut. These pass-through (PT) edges may also interact with the cut. However, even the ordinary PT edges require a register, and so must be accommodated in any colouring scheme.

**Definition 11.** The lifetime  $\mathcal{L}$  of an edge (n, n') is the number of cuts over which it spans:

$$\mathcal{L}(n, n') = \mathcal{D}(n) - \mathcal{D}(n')$$

**Definition 12.** An edge  $(n, n') \in E_V$  is a Pass Through (PT) edge over cut S of depth d when:

$$\mathcal{D}(n) > d > \mathcal{D}(n')$$

A Used Pass Through (UPT) edge is a PT edge from a node which is also used by one or more nodes in S, i.e. there is  $n'' \in S$  with  $(n, n'') \in E_V$ .

In particular, PT (and to a lesser extent UPT) edges are ideal candidates for spilling when transforming a cut. The next section discusses this further.

#### 5.4 Register Allocation

In order to colour the graph successfully with  $\mathcal{R}$  target machine registers no cut of the graph must be wider (*i.e.* the number of live registers) than the number of target registers available.

For every cut of depth d calculate  $W_{in}(d)$ . Then, while  $\mathcal{R} > |W_{in}(d)|$  we apply three transformations to the VSDG in increasing order of cost: (i) node raising (code motion), (ii) node cloning (undoing CSE), or (iii) node spilling, where we first choose non-loop nodes followed by loop nodes.

The first—node raising—pushes a node up to the next cut by adding serializing edges from all other nodes in the cut. We repeat this until either the liveness width is less than the number of physical registers, or there is only one node left in the cut.

In node cloning, we take a node and generate copies (clones). Serializing edges are added to maintain the DFR of the the clones. A simple algorithm for this transformation is to produce as many clones as there are dependents of the node; a node recombining pass will recombine clones that end up in the same cut.

Node cloning is not always applicable as it may increase the liveness width of higher cuts (when the in-registers of the cloned node did not previously pass

through the cut); placing a cloned node in a lower cut can increase the liveness width. But, used properly [18], node cloning can reduce the liveness width of lower cuts by splitting the live range of a node, which potentially has a lower cost than spilling.

Finally, when all other transformations are unable to satisfy the constraint, we must spill one or more edges to memory. PT edges are ideal candidates for spilling, as the lifetime of the edge affords good pipeline behaviour on superscalar RISC-like targets; likewise, UPT edges are similarly beneficial, but place some constraints on the location of the store node.

A related issue is the spilling of  $\theta$ -nodes. As discussed previously the worst-case cost of spilling a loop-variant variable from a  $\theta$ -node tuple is two stores and three loads, so these should always be done after spilling of PT nodes. By contrast, Chaitin/Chow colouring has to use approximate cost heuristics to decide to spill a variable in a loop or outside.

#### 6 Related Work

#### 6.1 Benefits over Other Program Graph Representations

The VSDG is based in part on the Value Dependence Graph (VDG) [21]. The VDG uses a  $\lambda$ -node to represent both functions and loop bodies, thereby combining loops and functions into one complex abstraction mechanism rather. In the VSDG we treat them separately with call and  $\theta$ -nodes. One particular problem the VDG has is that of preserving the terminating properties of a program—"Evaluation of the VDG may terminate even if the original program would not..." [21].

Another significant issue with the VDG is the process of generating target code from the VDG. The authors describe converting the VDG into a demand-based Program Dependence Graph (dPDG)—a normal Program Dependence Graph [9] with additional edges representing demand dependence—then converting that into a traditional control flow graph (CFG) [1] before finally generating target code from the CFG with a standard back-end code generator; this is not as flexible (or as clearly specified) as the VSDG presented in this paper.

Many other program graphs (with many and varied edge forms) have been presented in the literature: the Program Dependence Graph [9], the Program Dependence Web [2], the System Dependence Graph [11] and the Dependence Flow Graph [15]. Our VSDG is both simpler—only two types of edge represent all of the above flow information—and more normalizing (§3.3).

#### 6.2 Solving Phase Order Problems

The traditional view of register allocation as a graph colouring problem was proposed by Chaitin [5]. In §4.2 we generalise the both the Chaitin and Chow approaches.

Goodwin and Wilken [10] formulate global register allocation (including all possible spill placements) as a 0-1 integer programming problem. While they do

achieve quite impressive results, the cost is very high: the complexity of their algorithm is  $O(n^3)$  and for a given time period the allocator does not guarantee to allocate all functions.

Code motion as an optimization is not new (e.g. Partial Redundancy Elimination [14]). Perhaps the work closest in spirit to ours is that of Rüthing et al. [18] which presents algorithms for optimal placement of expressions and sub-expressions, combining both raising and lowering of code within basic blocks.

Most work has concentrated on the instruction scheduling/register allocation phase order problem, which we now consider.

The CRAIG framework [4], implemented within the ROCKET compiler [19], takes a brute force approach:

- 1. attempt register allocation after instruction scheduling,

- 2. if the schedule cost is not acceptable (by some defined metric) attempt register allocation before scheduling,

- 3. then while the cost is acceptable (*i.e.* there is some better schedule) add back in information from the first pass until the schedule just becomes too costly.

Their experience with an instance of CRAIG (CRAIG<sub>0</sub>) defines the metric as the existence of spill code. Their experimental results show improvements in execution time, but do not document the change in code size.

Rao [17] improves on  $CRAIG_0$  with additional heuristics to allow *some* spilling, where it can be shown that spilling has a beneficial effect.

Touati's thesis [20] argues that register allocation is the primary determinant of performance, not scheduling. The goal of his thesis is again to minimize the insertion of spill-code, both through careful analysis of register pressure, and by adding serializing edges to each basic block data dependency DAG. It is basic-block-based.

An early attempt at combining register allocation with instruction scheduling was proposed by Pinter [16]. That work is based on an instruction level register-based intermediate code, and is preceded by a phase to determine data dependencies. This dependence information then drives the allocator, generating a Parallelizable Interference Graph to suggest possible register allocations. Further, the Global Scheduling Graph is then used to schedule instructions within a region.

Another region-based approach is that of Janssen and Corporaal [12], where regions correspond to the bodies of natural loops. They then use this hierarchy of nested regions to focus register allocation, with the inner-most regions being favoured by better register allocation (*i.e.* less spill code).

The Resource Spackling Framework of Berson et al. [3] applies a Measure and Reduce paradigm to combine both phases—their approach first measures the resource requirements of a program using a unified representation, and then moves instructions out of excessive sets into resource holes. This approach is basic-block-based: a local scheduler attempts to satisfy the target constraints without increasing the execution time of a block; the more complicated global scheduler moves instructions between blocks.

#### 7 Conclusions and Further Work

In this paper we have defined the VSDG, an enhanced form of the VDG which includes state dependency edges to model sequentialized computation. By adding sufficient state-dependency edges we have shown that the VSDG is able to represent a single CFG; conversely fewer serializing edges relax the artificial constraints imposed by the CFG.

From this basis, we have shown that the VSDG framework supports a combined approach to register allocation and code motion, using an incremental algorithm which effectively interleaves the two phases, and thus avoiding the well-known phase-ordering problem. We have described an algorithm which, when given a well-formed, normalized VSDG then allocates registers, if necessary interleaving this with code motion, node splitting and register spilling.

The work presented here is the start of a larger project: an implementation of the algorithms in this paper is in progress.

Acknowledgements. The research reported here was supported with a grant from ARM Ltd. Thanks are due to Alistair Turnbull and Eben Upton for constructive debate on aspects of the VSDG, to Lee Smith for useful comments on an early draft of this paper, and to Mooly Sagiv and Tom Reps for helpful discussions at SAS'02.

### References

- AHO, A. V., SETHI, R., AND ULLMAN, J. D. Compilers: Principles, Techniques and Tools. Addison Wesley, 1986.

- Ballance, R. A., Maccabe, A. B., and Ottenstein, K. J. The program dependence web: A representation supporting control-, data-, and demand-driven interpretation of imperative languages. In *Proc. Conf. Prog. Lang. Design and Implementation (PLDI'90)* (June 1990), ACM, pp. 257–271.

- 3. Berson, D. A., Gupta, R., and Soffa, M. L. Resource spackling: A framework for integrating register allocation in local and global schedulers. Tech. rep., Dept. Computer Science, University of Pittsburgh, February 1994.

- 4. Brasier, T. S., Sweany, P. H., Beaty, S. J., and Carr, S. Craig: A practical framework for combining instruction scheduling and register assignment. In *Proc. Intl. Conf. Parallel Architectures and Compilation Techniques (PACT'95)* (Limassol, Cyprus, June 1995).

- CHAITIN, G. Register allocation and spilling via graph coloring. ACM SIGPLAN Notices 17, 6 (June 1982), 98–105.

- CHOW, F. C., AND HENNESSY, J. L. The priority-based coloring approach to register allocation. ACM Trans. Prog. Lang. and Syst. 12, 4 (October 1990), 501– 536.

- CLICK, C. From quads to graphs: an intermediate representation's journey. Tech. Rep. CRPC-TR93366-S, Center for Research on Parallel Computation, Rice University, October 1993.

- 8. Cytron, R. K., Ferrante, J., Rosen, B. K., Wegman, M. N., and Zadeck, F. K. Efficiently computing the static single assignment form and the control dependence graph. *ACM Trans. Programming Languages and Systems* 12, 4 (October 1991), 451–490.

- FERRANTE, J., OTTENSTEIN, K. J., AND WARREN, J. D. The program dependence graph and its use in optimization. ACM Trans. Prog. Lang. and Syst. 9, 3 (July 1987), 319–349.

- GOODWIN, D. W., AND WILKEN, K. D. Optimal and near-optimal global register allocation using 0-1 integer programming. Software—Practice and Experience 26, 8 (August 1996), 929–965.

- HORWITZ, S., REPS, T., AND BINKLEY, D. Interprocedural slicing using dependence graphs. ACM Trans. Prog. Langs and Systems 12, 1 (January 1990), 26–60.

- 12. Janssen, J., and Corporaal, H. Registers on demand: an integrated region scheduler and register allocator. In *Proc. Conf. on Compiler Construction* (April 1998).

- 13. JOHNSON, N. *tri*VM Intermediate Language Reference Manual. Tech. Rep. UCAM-CL-TR-529, University of Cambridge Computer Laboratory, 2002.

- 14. Morel, E., and Renvoise, C. Global optimization by suppression of partial redundancies. *Comm. ACM* 22, 2 (February 1979), 96–103.

- PINGALI, K., BECK, M., JOHNSON, R., MOUDGILL, M., AND STODGHILL, P. Dependence flow graphs: An algebraic approach to program dependencies. In *Proc.* 18th ACM Symp. on Principles of Prog. Langs (POPL) (January 1991), ACM, pp. 67–78.

- 16. PINTER, S. S. Register allocation with instruction scheduling: A new approach. In *Proc. ACM SIGPLAN Conference on Prog. Lang. Design and Implementation* (Albuquerque, NM, June 1993), pp. 248–257.

- 17. RAO, M. P. Combining register assignment and instruction scheduling. Master's thesis, Michigan Technological University, 1998.

- 18. RÜTHING, O., KNOOP, J., AND STEFFEN, B. Sparse code motion. In *Proc. 27th ACM SIGPLAN-SIGACT Symp. Principles of Prog. Langs (POPL)* (Boston, MA, 2000), ACM, pp. 170–183.

- 19. SWEANY, P., AND BEATY, S. Post-compaction register assignment in a retargetable compiler. In *Proc. 23rd Annual Workshop on Microprogramming and Microarchitecture* (November 1990), pp. 107–116.

- 20. TOUATI, S.-A.-A. Register Pressure in Instruction Level Parallelism. PhD thesis, Université de Versailles Saint-Quentin, June 2002.

- 21. Weise, D., Crew, R. F., Ernst, M., and Steensgaard, B. Value dependence graphs: Representation without taxation. In *ACM SIGPLAN-SIGACT Symp. on Principles of Prog. Langs (POPL)* (January 1994), ACM.

## Early Control of Register Pressure for Software Pipelined Loops

Sid-Ahmed-Ali Touati and Christine Eisenbeis

INRIA Rocquencourt, 78153 Le Chesnay, France {Sid-Ahmed-Ali.Touati, Christine.Eisenbeis}@inria.fr

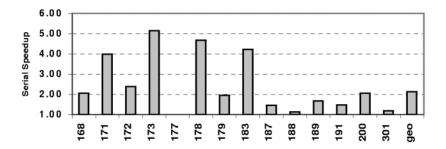

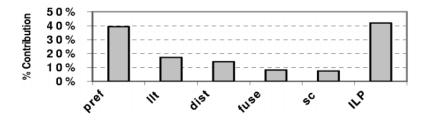

Abstract. The register allocation in loops is generally performed after or during the software pipelining process. This is because doing a conventional register allocation at first step without assuming a schedule lacks the information of interferences between variable lifetime intervals. Thus, the register allocator may introduce an excessive amount of false dependences that reduce dramatically the ILP (Instruction Level Parallelism). We present a new framework for controlling the register pressure before software pipelining. This is based on inserting some anti-dependences edges (register reuse edges) labeled with reuse distances, directly on the data dependence graph. In this new graph, we are able to guarantee that the number of simultaneously alive variables in any schedule does not exceed a limit. The determination of register and distance reuse is parameterized by the desired critical circuit ratio (MII) as well as by the register pressure constraints either can be minimized while the other one is fixed. After scheduling, register allocation is done cyclically on conventional register sets or on rotating register files. We give an optimal exact model, and another approximative one that generalizes the Ning-Gao [13] buffer optimization heuristics.

#### 1 Introduction

This article addresses the problem of register pressure in simple loop data dependence graphs (DDGs), with multiple register types and non unit assumed latencies operations. Our aim is to decouple the registers constraints and allocation from the scheduling process and to analyze the trade-off between memory (register pressure) and parallelism constraints, measured as the critical ratio  $MII^1$  of the DDG.

The principal reason is that we believe that register allocation is more important as an optimization issue than code scheduling. This is because the code performance is far more sensitive to memory accesses than to fine-grain scheduling (memory gap): a cache miss may inhibit the processor from achieving a high dynamic ILP, even if the scheduler has extracted it at compile time. Even if someone would expect that spill codes exhibit high locality, and hence would likely produce cache hits, we cannot assert it at compile time. The authors in [6] related that about 66% of application execution times are spent to satisfying memory requests.

Another reason for handling register constraints prior to ILP scheduling is that register constraints are much more complex than resource constraints. Scheduling under resource

$<sup>^{1}</sup>$  We refer here to  $MII_{dep}$  since we will not consider any resource constraints.

constraints is a performance issue. Given a DDG, we are sure to find at least one valid schedule for any underlying hardware properties (a sequential schedule in extreme case, i.e., no ILP). However, scheduling a DDG with a limited number of registers is more complex. We cannot guarantee the existence of at least one schedule. In some cases, we must introduce spill code and hence we change the problem (the input DDG). Also, a combined pass of scheduling with register allocation presents an important drawback if not enough registers are available. During scheduling, we may need to insert load-store operations. We cannot guarantee the existence of a valid issue time for these introduced memory access in an already scheduled code; resource or data dependence constraints may prevent from finding a valid issue slot inside an already scheduled code. This forces to iteratively apply scheduling followed by spilling until reaching a solution.

All the above arguments make us re-think new ways of handling register pressure before starting the scheduling process, so that the scheduler would be free from register constraints and would not suffer from excessive serializations.

Existing techniques in this field usually apply register allocation after a step of software pipelining that is sensitive to register requirement. Indeed, if we succeed in building a software pipelined schedule that does not produce more than R values simultaneously alive, then we can build a cyclic register allocation with R available registers [3,14]. We can use either loop unrolling [3], inserting move operations [8], or a hardware rotating register file when available  $[14]^2$ . Therefore, a great amount of work tries to schedule a loop such that it does not use more than R values simultaneously alive [9,23,13,15,12,5,16,7,10]. In this paper we directly work on the loop DDG and modify it in order to satisfy the register constraints for any further subsequent software pipelining pass. This idea is already present in [1] for DAGs and use the concept of *reuse* edge or vector developed in [18,19].

Our article is organized as follows. Sect. 2 defines our loop model and a generic ILP processor. Sect. 3 starts the study with a simple example. The problem of cyclic register allocation is described in Sect. 4 and formulated with integer linear programming (intLP). The special case where a rotating register file (RRF) exists in the underlying processor is discussed in Sect. 5. In Sect.6, we present a polynomial subproblem. Finally, we synthesize our experiments in Sect. 7 before concluding.

#### 2 Loop Model

We consider a simple innermost loop (without branches). It is represented by a graph  $G=(V,E,\delta,\lambda)$ , such that: V is the set of the statements in the loop body and E is the set of precedence constraints (flow dependences, or other serial constraints). We associate to each arc  $e\in E$  a latency  $\delta(e)$  in terms of processor clock cycles and a distance  $\lambda(e)$  in terms of number of iterations. We denote by u(i) the instance of the statement  $u\in V$  of the iteration i. A valid schedule  $\sigma$  must satisfy:

$$\forall e = (u, v) \in E : \sigma(u(i)) + \delta(e) \le \sigma(v(i + \lambda(e)))$$

<sup>&</sup>lt;sup>2</sup> Insertion of *move* operations or using a rotating register file requires R+1 registers at most [3].

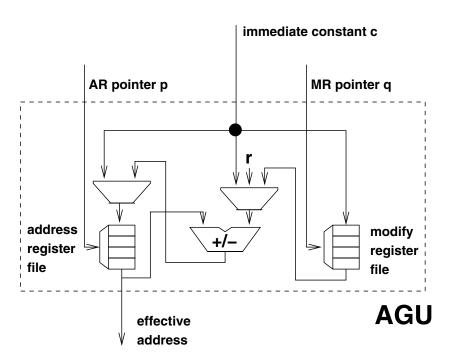

We consider a target RISC-style architecture with multiple register types, where  $\mathcal{T}$  denotes the set of register types (for instance,  $\mathcal{T}=\{int,float\}$ ). We make a difference between statements and precedence constraints, depending if they refer to values to be stored in registers or not.  $V_{R,t}$  is the set of values to be stored in registers of type  $t\in\mathcal{T}$ . We consider that each statement  $u\in V$  writes into at most one register of a type  $t\in\mathcal{T}$ . The statements which define multiple values with different types are accepted in our model if they do not define more than one value of a certain type.  $E_{R,t}$  is the set of flow dependence edges through a value of type  $t\in\mathcal{T}$ . The set of consumers (readers) of a value  $u^t$  is then the set:

$$Cons(u^t) = \{ v \in V \mid (u, v) \in E_{R,t} \}$$

To consider static issue VLIW and EPIC/IA64 processors in which the hardware pipeline steps are visible to compilers (we consider dynamically scheduled superscalar processors too), we assume that reading from and writing into a register may be delayed from the beginning of the schedule time, and these delays are visible to the compiler (architectural visible). We define two delay (offset) functions  $\delta_{r,t}$  and  $\delta_{w,t}$  in which: the read cycle of  $u^t$  from a register of type t is  $\sigma(u) + \delta_{r,t}(u)$ , and the the write cycle of  $u^t$  into a register of type t is  $\sigma(u) + \delta_{w,t}(u)$ .

For superscalar and EPIC/IA64 processors,  $\delta_{r,t}$  and  $\delta_{w,t}$  are equal to zero.

A software pipelining is a function  $\sigma$  that assigns to each statement u a scheduling date (in terms of clock cycle) that satisfies at least the precedence constraints. It is defined by an initiation interval, noted II, and the scheduling date  $\sigma_u$  for the operations of the first iteration. The operation u(i) of iteration i is scheduled at time  $\sigma_u + (i-1) \times II$ . For all edge  $e = (u, v) \in E$ , this periodic schedule must satisfy:

$$\sigma_u + \delta(e) \le \sigma_v + \lambda(e).II$$

Classically, by adding all such inequalities on any circuit C of G, we find that II must be greater than or equal to  $\max_{C} \frac{\sum_{e \in C} \delta(e)}{\sum_{e \in C} \lambda(e)}$ , that we commonly denote as MII (minimal initiation interval).

We consider now a number of available registers  $\rho$  and all the schedules that have no more than  $\rho$  simultaneously alive variables. Any actual following register allocation will induce new dependences in the DDG. Hence, register pressure has influence on the expected II, even if we assume unbounded resources. What we want to analyze here is the minimum II that can be expected for any schedule using less than  $\rho$  registers. We will denote this value as  $MII(\rho)$  and we will try to understand the relationship between  $MII(\rho)$  and  $\rho$ . Let us start by an example to fix the ideas.

#### 3 Basic Ideas

We give now more intuitions to the new edges that we add between couples of operations. These edges represent possible reuse by the second operation of the register released by the first operation. This can be viewed as a variant of [1] or [18,19].

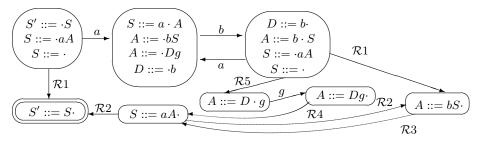

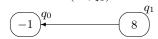

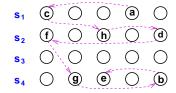

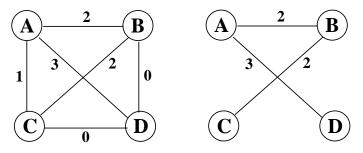

Let us consider a simple loop that consists of a unique flow dependence from u to v with distance  $\lambda=3$  (see Fig. 1.(a) where values to be stored in registers of the considered type are in bold circles, and flows are in bold edges). If we have an unbounded number of registers, all iterations of this loop can be run in parallel since there is no recurrence circuit in the DDG. At each iteration, operation u writes into a new register. Now, let

Fig. 1. Simple Example

us assume that we only have  $\rho=5$  available registers. The different instances of u can use only  $\rho=5$  registers to cyclically carry their results. In this case, the operation  $u(i+\rho)$  writes into the same register previously used by u(i). This fact creates an anti-dependence from  $v(i+\lambda)$ , which reads the value defined by u(i), to  $u(i+\rho)$ ; this means an anti-dependence in the DDG from v to u with a distance  $\rho-\lambda=2$ . Since u actually writes into its destination register  $\delta_{w,t}(u)$  clock cycles after it is issued and v reads it  $\delta_{r,t}(v)$  after it is issued, the latency of this anti-dependence is set to  $\delta_{r,t}(v)-\delta_{w,t}(u)$  for VLIW or EPIC codes, and to 1 for superscalar (sequential) codes. Consequently, the DDG becomes cyclic because of storage limitations (see Fig. 1.(b), where the anti-dependence is dashed). The introduced anti-dependence, also called "Universal Occupancy Vector' '(UOV) in [18], must in turn be counted when computing the new minimum initiation interval since a new circuit is created.

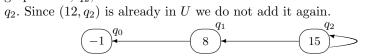

When an operation defines a value that is read by more than one operation, we cannot know in advance which of these consumers actually kills the value (which is the last reader), and hence we cannot know in advance when a register is freed. We propose a trick which defines for each value  $u^t$  of type t a fictitious killing task  $k_{u^t}$ . We insert an edge from each consumer  $v \in Cons(u^t)$  to  $k_{u^t}$  to reflect the fact that this killing task is scheduled after the last scheduled consumer (see Fig. 2). The latency of this serial edge is set to  $\delta_{r,t}(v)$  because of the reading delay, and we set its distance to  $-\lambda$  where  $\lambda$  is the distance of the flow dependence between u and its consumer v. This is done to model the fact that the operation  $k_{u^t}(i+\lambda-\lambda)$ , i.e.,  $k_{u^t}(i)$  is scheduled when the value  $u^t(i)$  is killed. The iteration number i of the killer of u(i) is only a convention and can be changed by retiming [11], without changing the nature of the problem.

Now, a register allocation scheme consists of defining the edges and the distances of reuse. That is, we define for each u(i) the operation v and iteration  $\mu_{u,v}$  such that  $v(i+\mu_{u,v})$  reuses the same destination register as u(i). This reuse creates a new anti-dependence from  $k_u$  to v with latency equal to  $-\delta_{w,t}(v)$  for VLIW or EPIC codes, and to 1 for sequential superscalar codes. The distance  $\mu_{u,v}$  of this edge has to be defined.

We will see in a further section that the register requirement can be expressed in terms of  $\mu_{u,v}$ .

Fig. 2. Killing Tasks

Hence, controlling register requirement means, first, determining which operation should reuse the register killed by another operation (where should anti-dependences be added?). Secondly, we have to determine variable lifetimes, or equivalently register requirement (how many iterations later ( $\mu$ ) should reuse occur)? The lower is the  $\mu$ , the lower is the register requirement, but also the larger is the MII.

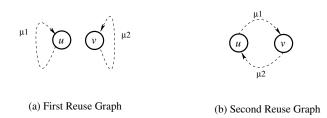

Fig. 2.(a) presents a first reuse decision where each statement reuses the register freed by itself. This is illustrated by adding an anti-dependence from  $k_u$  (resp.  $k_v$ ) to u (resp. v) with an appropriate distance  $\mu$ , as we will see later. Another reuse decision (see Fig. 2.(b)) may be that the statement u (resp. v) reuses the register freed by v (resp. u). This is illustrated by adding an anti-dependence from  $k_u$  (resp.  $k_v$ ) to v (resp. u). In both cases, the register requirement is  $\mu_1 + \mu_2$ , but it is easy to see that the two schemes do not have the same impact on MII: intuitively it is better that the operations share registers instead of using two different pools of registers. The next section gives a formal definition of the problem and provides an exact formulation.

#### 4 Problem Description

#### 4.1 Data Dependences and Reuse Edges

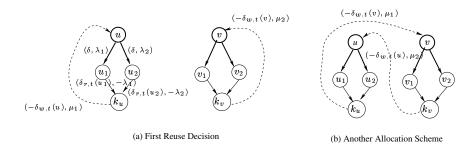

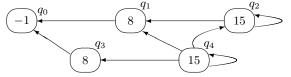

The reuse relation between the values (variables) is described by defining a new graph called a reuse graph that we note  $G^r = (V_{R,t}, E_r, \mu)$ . Fig. 3.(a) shows the first reuse decision where u (v resp.) reuses the register used by itself  $\mu_1$  ( $\mu_2$  resp.) iterations earlier. Fig. 3.(b) is the second reuse choice where u (v resp.) reuses the register used by v (u resp.)  $\mu_1$  ( $\mu_2$  resp.) iterations earlier. Each edge  $e = (u, v) \in E_r$  with a distance  $\mu(e)$  in the reuse graph means that there is an anti-dependence between  $k_u$  and v with a distance  $\mu(e)$ . The resulted DDG after adding the killing tasks and the anti-dependences to apply the register reuse decisions is called the DDG associated with a reuse decision: Fig. 2.(a) is the associated DDG with Fig. 3.(a), and Fig. 2.(b) is the one associated with Fig. 3.(b). We denote by  $G_{\rightarrow r}$  the DDG associated to a reuse decision r.

Fig. 3. Reuse Graphs

A reuse graph must verify some constraints to be valid: first, the resulting DDG must be schedulable; second, each value reuses only one freed register, and each register is reused by only one value. The second constraint means that the reuse scheme is the same at each iteration. Generalizing this condition by allowing different (but periodic) reuse schemes is beyond the scope of this paper. This condition results in the following lemma

**Lemma 1.** [22] Let  $G^r = (V_{R,t}, E_r, \mu)$  be a valid reuse graph of type t associated with a loop  $G = (V, E, \delta, \lambda)$ . Then:

- the reuse graph only consists of elementary and disjoined circuits;

- any value  $u^t \in V_{R,t}$  belongs to a unique circuit in the reuse graph.

Any circuit C in a reuse graph is called a *reuse circuit*. We note  $\mu(C)$  the sum of the  $\mu$  distances in this circuit. Then, to each reuse circuit  $C=(u_0,u_1,...,u_n,u_0)$ , there exists an image  $C'=(u_0\leadsto k_{u_0},u_1,...,u_n\leadsto k_{u_n},u_0)$  for it in the associated DDG. For instance in Fig. 2.(a),  $C'=(v,v_1,k_v,v)$  is an image for the reuse circuit C=(v,v) in Fig. 3.(a). Such image may not be unique.

If a reuse graph is valid, we can build a cyclic register allocation in the DDG associated with it, as explained in the following theorem. We require  $\mu(G^r)$  registers, in which  $\mu(G^r)$  is the sum of all  $\mu$  distances in the reuse graph  $G^r$ .

**Theorem 1.** [22] Let  $G = (V, E, \delta, \lambda)$  be a loop and  $G^r = (V_{R,t}, E_r, \mu)$  a valid reuse graph of a register type  $t \in \mathcal{T}$ . Then the reuse graph  $G^r$  defines a cyclic register allocation for G with exactly  $\mu_t(G^r)$  registers of type t if we unroll the loop  $\alpha$  times where :

$$\alpha = lcm(\mu_t(C_1), \cdots, \mu_t(C_n))$$

with  $C = \{C_1, \dots, C_n\}$  is the set of all reuse circuits, and lcm is the least common multiple.

For a complete and detailed proof, please refer to [22].

As a corollary, we can build a cyclic register allocation for all register types.

**Corollary 1.** [22] Let  $G = (V, E, \delta, \lambda)$  be a loop with a set of register types  $\mathcal{T}$ . To each type  $t \in \mathcal{T}$  is associated a valid reuse graph  $G_t^r$ . The loop can be allocated with  $\mu_t(G^r)$  registers for each type t if we unroll it  $\alpha$  times, where

$$\alpha = lcm(\alpha_{t_1}, \cdots, \alpha_{t_n})$$

where  $\alpha_{t_i}$  is the unrolling degree of the reuse graph of type  $t_i$ .

It should be noted that the fact that the unrolling factor may be significantly high is not related to our method and would happen only if we actually want to allocate the variables on this minimal number of registers with the computed reuse scheme. However, there may be other reuse schemes for the same number of registers, or there may be other available registers in the architecture. In that case, the meeting graph framework [3] can help to control or reduce this unrolling factor.

From all above, we deduce a formal definition of the problem of optimal cyclic register allocation with minimal ILP loss. We call it Schedule Independent Register Allocation (SIRA).

Problem 1 (SIRA). Let  $G = (V, E, \delta, \lambda)$  be a loop and  $\mathcal{R}_t$  the number of available registers of type t. Find a valid reuse graph for each register type such that the corresponding

$$\mu_t(G^r) \leq \mathcal{R}_t$$

and the critical circuit in G is minimized.

This problem can be reduced to the classical NP-complete problem of minimal register allocation [22]. The following section gives an exact formulation of SIRA.

#### 4.2 Exact Formulation

In this section, we give an intLP model for solving SIRA. It is built for a fixed execution rate II (the new constrained MII). Note that II is not the initiation interval of the final schedule, since the loop is not already scheduled. II denotes the value of the new desired critical circuit. Here, we assume VLIW or EPIC codes. For superscalar ones, we only have to set the anti-dependence latency to 1.

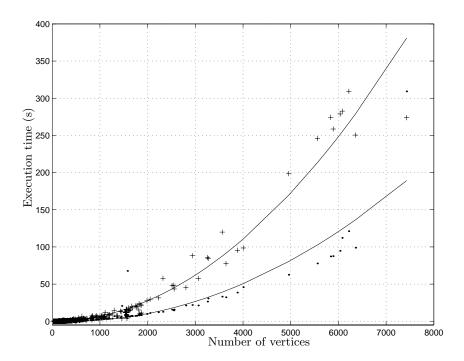

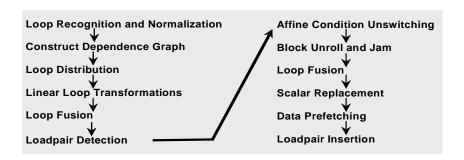

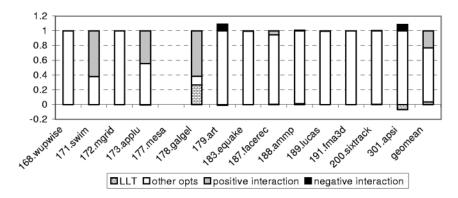

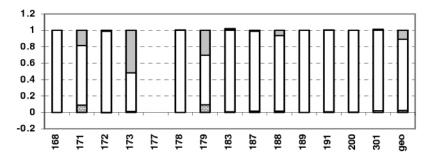

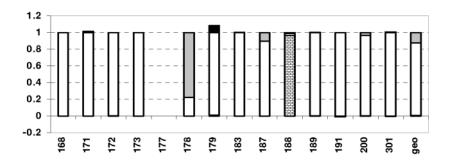

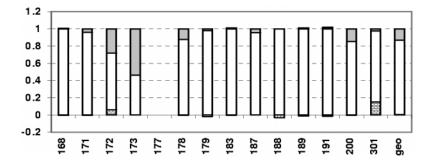

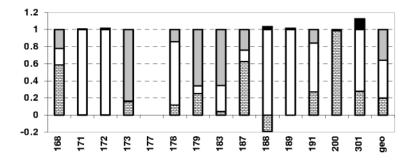

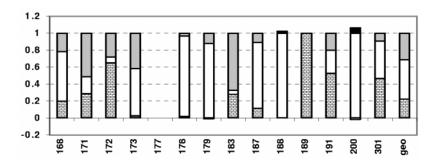

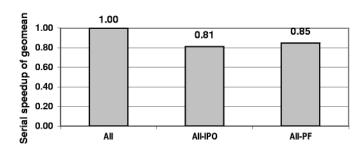

Our SIRA exact model uses the linear formulation of the logical implication ( $\Longrightarrow$ ) and equivalence ( $\Longleftrightarrow$ ) by introducing binary variables, as previously explained in [20, 21,22]. The size of our system is bounded by  $\mathcal{O}(|V|^2)$  variables and  $\mathcal{O}(|E|+|V|^2)$  linear constraints.